# Integrated Circuits and Logic Operations Based on Single-Layer MoS<sub>2</sub>

## Branimir Radisavljevic, Michael Brian Whitwick, and Andras Kis\*

Electrical Engineering Institute, Ecole Polytechnique Fédérale de Lausanne, Lausanne, Switzerland

wo-dimensional materials<sup>1</sup> are extremely interesting as building blocks of next-generation nanoelectronic devices for simple geometric reasons. It is in principle much easier to fabricate circuits and other complex structures by tailoring 2D lavers into desired forms than to deposit or grow nanowires or nanotubes with predictable electrical properties in predefined positions. Because of their atomic scale thickness, two-dimensional materials also offer a higher degree of electrostatic control than bulk materials,<sup>2</sup> making them interesting for fabrication of low-power electronic devices.<sup>3</sup> Without any doubt, the most widely studied two-dimensional material to date is graphene,<sup>4</sup> due to its high intrinsic low-temperature mobility of at least  $200\,000\,\text{cm}^2/(\text{V s})$ ,<sup>5</sup> the presence of massless Dirac fermions,<sup>6</sup> and a wealth of interesting physical phenomena such as the fractional quantum Hall effect.<sup>7</sup> In its untreated form however, graphene has no band gap, resulting in small current on/off ratios in graphene field effect transistors. Graphene band gaps up to 400 meV have been introduced by shaping them into ribbons<sup>8,9</sup> or applying high transverse electric fields to bilayer graphene.<sup>10,11</sup> This not only increases complexity but also results in significant mobility reduction or loss of coherence<sup>12</sup> or requires voltages exceeding 100 V.<sup>10</sup> Because of this, it is very difficult to build logic circuits based on graphene that would operate at room temperature with low stand-by power dissipation.

Logic circuits and the ability to amplify electrical signals form the functional backbone of electronics along with the possibility to integrate multiple elements on the same chip. Here, we demonstrate that single-layer MoS<sub>2</sub>, a two-dimensional semiconductor with a direct band gap of 1.8 eV (ref 13), has the capability to amplify signals and perform basic logic operations in simple integrated circuits composed of two MoS<sub>2</sub> transistors.<sup>3</sup> Our integrated circuit is

#### ABSTRACT

Logic circuits and the ability to amplify electrical signals form the functional backbone of electronics along with the possibility to integrate multiple elements on the same chip. The miniaturization of electronic circuits is expected to reach fundamental limits in the near future. Two-dimensional materials such as single-layer MoS<sub>2</sub> represent the ultimate limit of miniaturization in the vertical dimension, are interesting as building blocks of low-power nanoelectronic devices, and are suitable for integration due to their planar geometry. Because they are less than 1 nm thin, 2D materials in transistors could also lead to reduced short channel effects and result in fabrication of smaller and more power-efficient transistors. Here, we report on the first integrated circuit based on a two-dimensional semiconductor MoS<sub>2</sub>. Our integrated circuits are capable of operating as inverters, converting logical "1" into logical "0", with room-temperature voltage gain higher than 1, making them suitable for incorporation into digital circuits. We also show that electrical circuits composed of single-layer MoS<sub>2</sub> transistors are capable of performing the NOR logic operation, the basis from which all logical operations and full digital functionality can be deduced.

**KEYWORDS:** two-dimensional materials  $\cdot$  dichalcogenides  $\cdot$  MoS<sub>2</sub>  $\cdot$  nanoelectronic devices  $\cdot$  logic circuits  $\cdot$  digital electronics

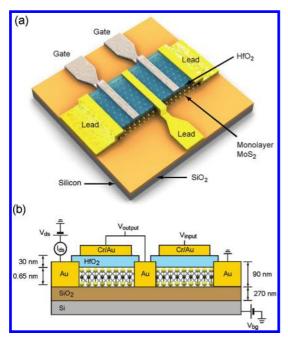

composed of two n-type transistors realized on the same two-dimensional crystal of monolayer MoS<sub>2</sub>, as schematically depicted in Figure 1a and b.

Single-layer  $MoS_2$  is a typical two-dimensional semiconductor from the layered transition metal dichalcogenide family. Single layers, 6.5 Å thick, can be extracted from bulk crystals using the micromechanical cleavage technique commonly associated with the production of graphene, <sup>1,14</sup> lithiumbased intercalation, <sup>15,16</sup> or liquid phase exfoliation<sup>17</sup> and used as ready-made blocks for electronics.<sup>3</sup> Decreasing the number of

\* Address correspondence to andras.kis@epfl.ch.

Received for review September 28, 2011 and accepted November 2, 2011.

Published online November 10, 2011 10.1021/nn203715c

RADISAVLJEVIC ET AL.

of © 2011 American Chemical Society

VOL. 5 • NO. 12 • 9934-9938 • 2011

Figure 1. Integrated circuit based on single-layer MoS<sub>2</sub> (not to scale). (a) Single-layer MoS<sub>2</sub> is deposited on top of a Si chip covered with 270 nm thick SiO<sub>2</sub>. The integrated circuit is composed of two transistors defined by a neighboring pair of leads and controlled by local gates with HfO<sub>2</sub> gate dielectric. (b) Cross-sectional view of the structure of a monolayer MoS<sub>2</sub> integrated circuit together with electrical connections used to characterize the device. One of the gold electrodes acts as drain while the other, source electrode is grounded. The monolayer is separated from the top gate by 30 nm of ALD-grown HfO2. The top gate width for the device is 4.7  $\mu$ m, top gate length is 1.3  $\mu$ m, and lead spacing is 1.6  $\mu$ m. The substrate can act as a back gate but is kept grounded during the measurement.

layers in mesoscopic MoS<sub>2</sub> structures leads to a transformation from an indirect band gap semiconductor with a band gap of 1.2 eV (ref 18) into a direct gap semiconductor,<sup>13,19-21</sup> with a band gap of 1.8 eV (ref 13) due to quantum confinement.<sup>21</sup> Being an ultrathin direct gap semiconductor, single-layer MoS<sub>2</sub> is very interesting as a material complementary to graphene that does not have a band gap in its pristine form. This makes it very difficult to fabricate logic circuits<sup>22,23</sup> or amplifiers<sup>24</sup> that would operate at room temperature with a voltage gain > 1, which is necessary for incorporating such structures in electronic circuits. The presence of a band gap in single-layer MoS<sub>2</sub> on the other hand allows the realization of field-effect transistors with room-temperature on/off ratios that can exceed 10<sup>8</sup> (ref 3), which makes them interesting for building logic devices with low power dissipation. Recent simulations also predict that short channel single-layer MoS<sub>2</sub> devices could have higher oncurrent density than those based on Si,<sup>25,26</sup> a current on/off ratio higher than 10<sup>10</sup>, a high degree of immunity to short channel effects<sup>2,27</sup> and abrupt switching.<sup>26</sup> All these properties show that MoS<sub>2</sub> could be an interesting material for future applications in nanoelectronics.

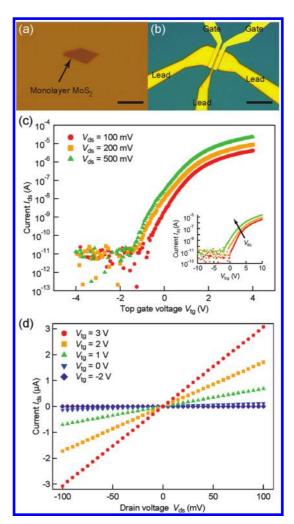

Figure 2. Electrical characterization of the integrated circuit based on monolayer MoS<sub>2</sub>. (a) Optical image of a monolayer MoS<sub>2</sub> deposited on top of a Si substrate with a 270 nm thick SiO<sub>2</sub> layer. (b) Integrated circuit based on the flake shown in (a). The device consists of three Au electrical leads that can act as source, drain, and output terminals and two local gates. The scale bars in (a) and (b) are 10  $\mu$ m long. (c) Drain-source current Ids through the MoS2 monolayer transistor on the left side of the integrated circuit shown in (b), measured as a function of the top gate voltage  $V_{ta}$ . The MoS<sub>2</sub> transistor shows gating response typical of FETs with n-type conducting channels. The inset shows the drain-source current I<sub>ds</sub> as a function of back gate voltage  $V_{\rm bg}$  for drain-source voltage  $V_{\rm ds}$  values of 100, 200, and 500 mV. Measurements were performed with floating top gate. (d) Drain-source current I<sub>ds</sub> as a function of drainsource voltage for different values of  $V_{tg}$ . The current through the device changes by over 6 orders of magnitude when the top gate voltage is swept in the -4 to +4 V range.

We begin our integrated circuit fabrication by exfoliating single-layer MoS<sub>2</sub>, Figure 2b, from bulk crystals using adhesive-tape-based micromechanical exfoliation,<sup>1,4</sup> commonly used for the production of graphene. Monolayers of MoS<sub>2</sub> are deposited on degenerately doped Si substrates covered with 270 nm thick SiO<sub>2</sub>, resulting in optimal contrast for optical detection of single layers.<sup>28</sup> Three electrical leads are first fabricated using standard electronbeam lithography, followed by deposition of 90 nm

VOL.5 • NO.12 • 9934-9938 • 2011

IAI

thick Au electrodes and annealing in an Ar/H<sub>2</sub> mixture<sup>29</sup> in order to remove resist residue and decrease contact resistance. The device is then covered by atomic layer deposition of 30 nm HfO<sub>2</sub>, a high- $\kappa$  material commonly used as a gate dielectric.<sup>30,31</sup> Finally, local top gates are deposited in the final round of e-beam lithography and metal deposition, resulting in an integrated circuit such as the one shown in Figure 2b, composed of two single-layer transistors connected in series. The channel width of the transistors in our integrated circuit is 4.2  $\mu$ m, lead spacing is 1.6  $\mu$ m, and top gate length is 1.3  $\mu$ m.

Both transistors in our integrated circuit can be independently controlled by applying a voltage  $V_{tq}$ to the corresponding top gate, which is one of the crucial requirements for constructing integrated circuits composed of multiple transistors realized on the same substrate. We characterize both transistors in our integrated circuit at room temperature by connecting a pair of neighboring leads to the source and ground terminals of a semiconductor parameter analyzer and a voltage  $V_{tg}$  to the corresponding top gate. The substrate is grounded throughout the measurements. The transfer characteristic for the transistor on the right side of the integrated circuit is shown in Figure 2c and is typical of n-type field-effect transistors. By changing the top gate voltage  $V_{tq}$  from -4 V to +4 V, we can modify the current through the device over several orders of magnitude thanks to the high current on/off ratio of our transistor, higher than 10<sup>6</sup> in this range of top gate voltage  $V_{tq}$ . The on-resistance is 24 k $\Omega$  for  $V_{\rm ds}$  = 100 mV and  $V_{\rm tg}$  = 4 V. The linear and symmetric  $I_{\rm ds}$ vs V<sub>ds</sub> characteristics shown in Figure 2d indicate that the contacts are ohmic. From back-gating characteristics, shown in the inset of Figure 2c, we estimate the twocontact low-field field-effect mobility of  $\sim$ 320 cm<sup>2</sup>/(V s). At the bias voltage  $V_{ds} = 500$  mV, the maximal measured on-current is 22  $\mu$ A (4.6  $\mu$ A/ $\mu$ m), with  $I_{on}/I_{off}$  higher than 10<sup>6</sup> for the  $\pm$ 4 V range of  $V_{tg}$  and an  $I_{off} \approx$  400 fA/ $\mu$ m.

The device transconductance defined as  $g_m = dI_{ds}/dV_{tg}$  is 12  $\mu$ S (2.6  $\mu$ S/ $\mu$ m) for  $V_{ds} = 500$  mV and is comparable to CdS nanoribbon array transistors (2.5  $\mu$ S/ $\mu$ m at  $V_{ds} = 1$  V).<sup>32</sup> High-performance top-gated graphene transistors can have normalized transconductance values<sup>33</sup> as high as 1.27 mS/ $\mu$ m, while carbon nanotubes can reach transconductance of 2.3 mS/ $\mu$ m.<sup>34</sup> We expect that lowering the channel length will reduce the number of scattering centers and increase the on-current in MoS<sub>2</sub>-based transistors. Theoretical models predict that MoS<sub>2</sub> transistors with a gate length of 15 nm would operate in the ballistic regime<sup>25,26</sup> with a maximum on-current as high as 1.6 mA/ $\mu$ m and a transconductance of 4 mS/ $\mu$ m, for both  $V_{tg} = 0.6$  V and a bias  $V_{ds} = 0.5$  V.<sup>26</sup>

The efficient channel switching for small voltages exhibited by our device is also clearly illustrated in Figure 2d, where we show the source-drain current

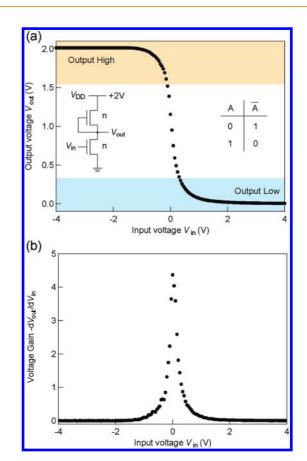

Figure 3. Characteristics of the integrated MoS<sub>2</sub> inverter. (a) Output voltage as a function of the input voltage. Schematic drawing of the electronic circuit and the truth table for the NOT logic operation (inset). (b) Dependence of the inverter gain (negative value of  $dV_{out}/dV_{in}$ ) on the input voltage. The maximal voltage gain above 4 indicates that our inverter is suitable for integration in arrays of logic devices.

$l_{ds}$  dependence on source—drain voltage  $V_{ds}$  for different values of top gate voltage  $V_{tg}$ . This large degree of control at room temperature is necessary for realizing logic operations with large voltage gain. For development of logic circuits based on new materials, a voltage gain > 1 is necessary so that the output of one logic gate could be used to drive the input of the next gate without the need for signal restoration.

We proceed by demonstrating that our single-layer  $MoS_2$  integrated circuit can operate as the most basic logic gate: a logic inverter, capable of converting a logical 0 (low input voltage) into logical 1 (high output voltage). We connect the middle lead to one of the local gates in a configuration depicted in the inset of Figure 3a, commonly used in logic circuits based on only one type (n or p) of transistor. In this configuration, the "lower" transistor acts as a switch, while the "upper" one acts as an active load. Input voltage  $V_{in}$  is applied to the local gate of the switch transistor while the supply voltage  $V_{dd} = 2 V$  is applied to the drain electrode of the load transistor. The output voltage and transfer characteristic of the inverter as a function of the input voltage  $V_{in}$  is shown in Figure 3a.

VOL.5 • NO.12 • 9934–9938 • 2011 🕰

agnanc www.acsnano.org

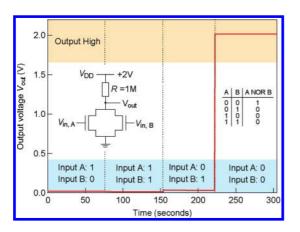

Figure 4. Demonstration of a NOR-gate logic circuit based on single-layer  $MoS_2$  transistors. The circuit is formed by connecting two monolayer  $MoS_2$  transistors in parallel and using an external 1 MOhm resistor as a load (left inset). The output voltage  $V_{out}$  is shown for four different combinations of input states (1,0), (1,1), (0,1), and (0,0). The output is in the high state only if both inputs are in the low state (truth table in the inset). All logic operations can be expressed as combinations of NOR operations.

For input voltages corresponding to logic 0, the switch transistor has a higher resistance than the load transistor and is effectively turned off. This results in a constant voltage at the output terminal, which is close to the supply voltage of  $V_{dd} = 2$  V applied to the load drain electrode. By increasing the input voltage above -1 V, the lower FET becomes more conductive and the output voltage  $V_{out}$  is now in the low range.

In the input voltage range of  $\pm 0.3$  V, the output of the inverter is changing faster than the input, indicating that our device is capable of amplifying signals. The voltage gain defined as the negative of  $dV_{out}/dV_{in}$ and plotted in Figure 3b is higher than 4. For successful implementation of digital logic in electronic circuits based on any new nanomaterial, a voltage gain > 1 is needed so that the output of one inverter could drive the input of the next inverter in the cascade. Our inverter has a voltage gain higher than 4 and is therefore suitable for integration in arrays of logic gates. This could involve level shifters because the input and output logic levels are not the same. Increasing the threshold voltage of MoS<sub>2</sub> transistors using for example substrate functionalization could also bring input and output voltages to the same level.

We note that to the best of our knowledge the maximal voltage gain for graphene-based inverters<sup>22</sup> demonstrated so far is 2–7 but at the temperature of 80 K,<sup>23,35</sup> due to the low band gap (<100 meV) in bilayer graphene, which prohibits the use of such devices at room temperature.

Our monolayer MoS<sub>2</sub> transistors can also be used to perform logic operations involving two operands. By connecting two transistors in parallel and using an external resistor as load, we can construct a NOR gate, shown in the inset of Figure 4, where we show the output voltage for all the possible input states of the NOR gate. When either one or both of the transistors are in the "on" state (corresponding to  $V_{in} = 2$  V), the output is ~0 V, corresponding to logical 0. Only when both transistors are in the "off" state does the output become logical 1 ( $V_{out} \approx V_{dd} = 2$  V). NOR operation forms a functionally complete set of binary operations: every possible logic operation (AND, OR, NAND, *etc.*) can be realized using a network of NOR gates.

### CONCLUSIONS

We have demonstrated here that single-layer MoS<sub>2</sub>, a new two-dimensional semiconductor, can be used as the material basis for fabrication of integrated circuits and for performing logic operations with room-temperature characteristics suitable for integration. Our work represents the critical first step in the implementation of digital logic in two-dimensional materials at room temperature. Together with the possibility of large-scale liquid-based processing of MoS<sub>2</sub> and related 2D materials,<sup>17</sup> our finding could open the way to using MoS<sub>2</sub> for applications in flexible electronics. Single-layer MoS<sub>2</sub> also has advantages over conventional silicon: it is thinner than state-of-the-art silicon films that are 2 nm thick<sup>36</sup> and has a smaller dielectric constant ( $\varepsilon$  = 7, ref 37) than silicon ( $\varepsilon$  = 11.9), implying that using single-layer MoS<sub>2</sub> could reduce short channel effects<sup>26</sup> and result in smaller and less powerhungry transistors than those based on silicon technology. Several difficulties however need to be solved before MoS<sub>2</sub> can become a mainstream electronic material for the semiconductor industry. A method for large-scale growth of continuous monolayers of MoS<sub>2</sub> or a similar 2D semiconductor will be needed to fabricate more complex integrated circuits with a large number of elements.

#### MATERIALS AND METHODS

Single layers of MoS<sub>2</sub> are exfoliated from commercially available crystals of molybdenite (SPI Supplies Brand Moly Disulfide) using the adhesive-tape micromechanical cleavage technique method pioneered for the production of graphene. AFM imaging is performed using the Asylum Research Cypher AFM. After Au contact deposition, devices are annealed in 100 sccm of Ar and 10 sccm H<sub>2</sub> flow at 200 °C for 2 h.<sup>29</sup> ALD is performed in a commercially available system (Beneq) using a reaction of H<sub>2</sub>O with tetrakis-(ethylmethylamido)hafnium. Electrical characterization is carried out using National Instruments DAQ cards and a home-built shielded probe station with micromanipulated probes.

VOL.5 • NO.12 • 9934-9938 • 2011

www.acsnano.org

Acknowledgment. Device fabrication was carried out in part in the EPFL Center for Micro/Nanotechnology (CMI). We thank S. Bertolazzi and D. Lembke for help with device fabrication, T. Heine and G. Seifert for useful discussions, K. Lister (CMI) for help with the e-beam lithography system, and A. Radenovic (EPFL) and D. Bouvet (CMI) for support with ALD deposition. This work was financially supported by ERC grant no. 240076 and the Swiss Nanoscience Institute (NCCR Nanoscience).

#### **REFERENCES AND NOTES**

- Novoselov, K. S.; Jiang, D.; Schedin, F.; Booth, T. J.; Khotkevich, V. V.; Morozov, S. V.; Geim, A. K. Two-Dimensional Atomic Crystals. *Proc. Natl. Acad. Sci. U. S. A.* 2005, 102, 10451–10453.

- Schwierz, F. Graphene Transistors. Nat. Nanotechnol. 2010, 5, 487–496.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6, 147–150.

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, 306, 666–669.

- Bolotin, K. I.; Sikes, K. J.; Jiang, Z.; Klima, M.; Fudenberg, G.; Hone, J.; Kim, P.; Stormer, H. L. Ultrahigh Electron Mobility in Suspended Graphene. *Solid State Commun.* 2008, 146, 351–355.

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Katsnelson, M. I.; Grigorieva, I. V.; Dubonos, S. V.; Firsov, A. A. Two-Dimensional Gas of Massless Dirac Fermions in Graphene. *Nature* **2005**, *438*, 197–200.

- Du, X.; Skachko, I.; Duerr, F.; Luican, A.; Andrei, E. Y. Fractional Quantum Hall Effect and Insulating Phase of Dirac Electrons in Graphene. *Nature* 2009, *462*, 192– 195.

- Han, M. Y.; Ozyilmaz, B.; Zhang, Y. B.; Kim, P. Energy Band-Gap Engineering of Graphene Nanoribbons. *Phys. Rev. Lett.* 2007, 98, 206805.

- Li, X.; Wang, X.; Zhang, L.; Lee, S.; Dai, H. Chemically Derived, Ultrasmooth Graphene Nanoribbon Semiconductors. *Science* 2008, *319*, 1229–1232.

- Zhang, Y.; Tang, T.-T.; Girit, C.; Hao, Z.; Martin, M. C.; Zettl, A.; Crommie, M. F.; Shen, Y. R.; Wang, F. Direct Observation of a Widely Tunable Bandgap in Bilayer Graphene. *Nature* 2009, 459, 820–823.

- 11. Xia, F.; Farmer, D. B.; Lin, Y.-m.; Avouris, P. Graphene Field-Effect Transistors with High On/Off Current Ratio and Large Transport Band Gap at Room Temperature. *Nano Lett.* **2010**, *10*, 715–718.

- Sols, F.; Guinea, F.; Neto, A. H. C. Coulomb Blockade in Graphene Nanoribbons. *Phys. Rev. Lett.* 2007, 99, 166803.

- Mak, K. F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. F. Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* **2010**, *105*, 136805.

- Frindt, R. F. Single Crystals of MoS<sub>2</sub> Several Molecular Layers Thick. J. App. Phys. **1966**, 37, 1928–1929.

- Joensen, P.; Frindt, R. F.; Morrison, S. R. Single-Layer MoS<sub>2</sub>. *Mater. Res. Bull.* **1986**, *21*, 457–461.

- Schumacher, A.; Scandella, L.; Kruse, N.; Prins, R. Single-Layer MoS<sub>2</sub> on Mica: Studies by Means of Scanning Force Microscopy. *Surf. Sci. Lett.* **1993**, *289*, L595–L598.

- Coleman, J. N.; Lotya, M.; O'Neill, A.; Bergin, S. D.; King, P. J.; Khan, U.; Young, K.; Gaucher, A.; De, S.; Smith, R. J.; *et al.* Two-Dimensional Nanosheets Produced by Liquid Exfoliation of Layered Materials. *Science* **2011**, *331*, 568–571.

- Kam, K. K.; Parkinson, B. A. Detailed Photocurrent Spectroscopy of the Semiconducting Group Vib Transition Metal Dichalcogenides. J. Phys. Chem. 1982, 86, 463–467.

- Lebegue, S.; Eriksson, O. Electronic Structure of Two-Dimensional Crystals from Ab Initio Theory. *Phys. Rev. B* 2009, *79*, 115409.

- Splendiani, A.; Sun, L.; Zhang, Y.; Li, T.; Kim, J.; Chim, C.-Y.; Galli, G.; Wang, F. Emerging Photoluminescence in Monolayer MoS<sub>2</sub>. *Nano Lett.* **2010**, *10*, 1271–1275.

- Kuc, A.; Zibouche, N.; Heine, T. Influence of Quantum Confinement on the Electronic Structure of the Transition Metal Sulfide TS<sub>2</sub>. *Phys. Rev. B* **2011**, *83*, 245213.

- Traversi, F.; Russo, V.; Sordan, R. Integrated Complementary Graphene Inverter. *Appl. Phys. Lett.* 2009, *94*, 223312.

- Li, S.-L.; Miyazaki, H.; Kumatani, A.; Kanda, A.; Tsukagoshi, K. Low Operating Bias and Matched Input–Output Characteristics in Graphene Logic Inverters. *Nano Lett.* 2010, 10, 2357–2362.

- Yang, X.; Liu, G.; Balandin, A. A.; Mohanram, K. Triple-Mode Single-Transistor Graphene Amplifier and Its Applications. ACS Nano 2010, 4, 5532–5538.

- Liu, L.; Kumar, S. B.; Ouyang, Y.; Guo, J. Performance Limits of Monolayer Transition Metal Dichalcogenide Transistors. *IEEE Trans. Electron Devices* 2011, 58, 3042–3047.

- Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer MoS<sub>2</sub> Transistors Be? *Nano Lett* **2011**, *11*, 3768–3773.

- 27. Schwierz, F. Nanoelectronics: Flat Transistors Get Off the Ground. *Nat. Nanotechnol.* **2011**, *6*, 135–136.

- Benameur, M. M.; Radisavljevic, B.; Heron, J. S.; Sahoo, S.; Berger, H.; Kis, A. Visibility of Dichalcogenide Nanolayers. Nanotechnology 2011, 22, 125706.

- Ishigami, M.; Chen, J. H.; Cullen, W. G.; Fuhrer, M. S.; Williams, E. D. Atomic Structure of Graphene on SiO<sub>2</sub>. Nano Lett. 2007, 7, 1643–1648.

- Bohr, M. T.; Chau, R. S.; Ghani, T.; Mistry, K., The High-K Solution. *IEEE Spectrum* Oct 2007, 44, 29–35.

- Mistry, K.; Allen, C.; Auth, C.; Beattie, B.; Bergstrom, D.; Bost, M.; Brazier, M.; Buehler, M.; Cappellani, A.; Chau, R.; et al. A 45nm Logic Technology with High-K+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-Free Packaging. *Tech. Dig.*—*Int. Electron Devices Meet.* 2007, 247–250.

- Duan, X.; Niu, C.; Sahi, V.; Chen, J.; Parce, J. W.; Empedocles, S.; Goldman, J. L. High-Performance Thin-Film Transistors Using Semiconductor Nanowires and Nanoribbons. *Nature* 2003, *425*, 274–278.

- Liao, L.; Lin, Y.-C.; Bao, M.; Cheng, R.; Bai, J.; Liu, Y.; Qu, Y.; Wang, K. L.; Huang, Y.; Duan, X. High-Speed Graphene Transistors with a Self-Aligned Nanowire Gate. *Nature* 2010, 467, 305–308.

- Wind, S. J.; Appenzeller, J.; Martel, R.; Derycke, V.; Avouris, P. Vertical Scaling of Carbon Nanotube Field-Effect Transistors Using Top Gate Electrodes. *Appl. Phys. Lett.* 2002, *80*, 3817.

- Li, S.-L.; Miyazaki, H.; Lee, M. V.; Liu, C.; Kanda, A.; Tsukagoshi, K. Complementary-Like Graphene Logic Gates Controlled by Electrostatic Doping. *Small* **2011**, *7*, 1552–1556.

- Gomez, L.; Aberg, I.; Hoyt, J. L. Electron Transport in Strained-Silicon Directly on Insulator Ultrathin-Body N-Mosfets with Body Thickness Ranging from 2 to 25 nm. *IEEE Electron Device Lett.* 2007, 28, 285–287.

- Frindt, R. F.; Yoffe, A. D. Physical Properties of Layer Structures: Optical Properties and Photoconductivity of Thin Crystals of Molybdenum Disulphide. *Proc. R. Soc. A* **1963**, 273, 69–83.

VOL.5 NO.12 9934-9938 2011